DDR5 内存接口的高效验证和调试

内存技术正在迅速发展 – 您的测量工具能满足需要吗?

5G 正在快速发展,并且正在推动各种激动人心的技术的发展 – 包括增强现实、人工智能、云计算和物联网。所有这些数据都需要存储在某个地方并以前所未有的速度进行访问,这意味着像 DDR5 这样的技术从未如此重要。DDR5 改善了带宽、密度和通道效率,但是更高的数据传输速率和更快的信号速度意味着复杂的设计将突破信号完整性的界限,并对合规性、调试和验证提出了更高的性能测量要求。

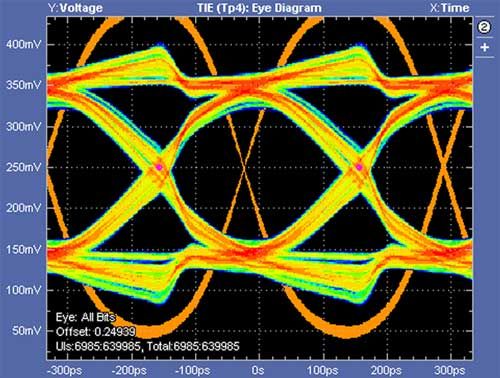

泰克 TekExpress DDR5 发射机解决方案是一种自动化的系统级测试应用,可让您快速、有效和可靠地验证和调试 DDR5 设计,以满足 JEDEC 定义的 50 多种电气和时序测量要求。

DFE分析

在存在符号间干扰 (ISI) 的情况下测试 DDR5 设计时,最佳的 DDR3/4 调试工具仍显不足。我们的 DDR5 系统级一致性软件提供了多种自动化工具来克服下一代 DDR 带来的挑战,其中包括:

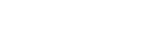

- 对突发 DDR5 流量进行写入数据眼图测量的 Rx DFE 均衡支持功能

- 对 JEDEC 定义的 50 多种 DDR5 电气和时序参数进行自动测量

- 可长期、稳定区分读写突发的新算法

- 新的一致性测试架构具有增强的自动化功能,可减少测试时间并帮助您更快地将设计推向市场

进行调试和验证

泰克的 LPDDR5 发射机解决方案将控制权归还给用户。用户自定义采集模式可让您通过自定义示波器设置(例如采样率、记录长度、带宽等)来运行 LPDDR5 JEDEC 一致性测量。

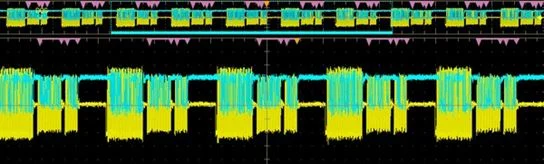

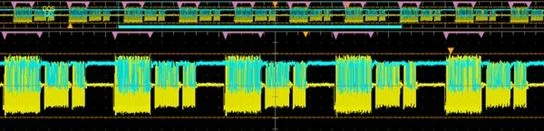

读/写突发分离一直是存储器验证工程师的主要问题。通常,在系统级别上,无法控制 DDR 总线上的数据流量。LPDDR5 发射机解决方案采用新的改进突发分离算法,不仅可以同时进行读/写突发检测,而且还可以缩短测试时间和提高准确性。

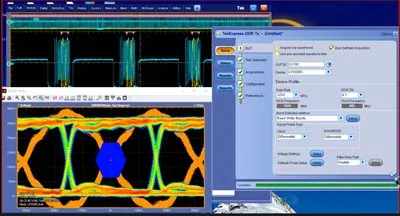

SDLA

在反嵌 LPDDR5 设计时,验证 S 参数通常是主要的考虑因素。借助改进的无源检查、端口分配和绘图功能,串行数据链路分析 (SDLA) 不仅增强了 S 参数文件的验证能力,而且还提高了灵活性,节省了时间并增加了对反嵌过程的信心。其他调试软件工具需要您完成整个过程才能找到结果。泰克的 LPDDR5 发射机解决方案可帮助您在早期阶段发现问题,从而提高调试效率并优化设计。SDLA 功能也可用于 DFE 分析。

有关更多信息,请在此查看我们的 SDLA 应用程序注释。

DDR5 电气验证和调试技术资料

The DDR (Dual Data Rate) is a dominant and fast-growing memory technology. It offers high data transfer rates required for virtually computing applications, from consumer products to the most powerful servers. The high speed of these signals requires high-performance measurement tools. The Tektronix TekExpress DDR Tx is an automated test application used to validate and debug the DDR5 designs of the DUT as per the JEDEC specifications. The solution enables you to achieve new levels of productivity, efficiency, and measurement reliability.

Key features

- Supports 52 measurements of DDR5 System Transmitter Tests as per DDR5 JEDEC specification:

- 21 Clock measurements

- 09 Write Burst measurements

- 01 Write Data Eye measurement

- 13 Read Burst measurements

- 08 Command and Address measurements

- User-Defined Acquisition (UDA) mode for Clock, Write Clock, CA, CS, Data Strobe, and data for both Write and Read traffic (or bursts).

UDA: The TekExpress DDR Tx ‘DDR5’ Transmitter Solution puts control back where it should be, with the user. User defined acquisition mode allows you to run DDR5 JEDEC compliance measurements by customizing scope settings like sample rate, record length, bandwidth, and more

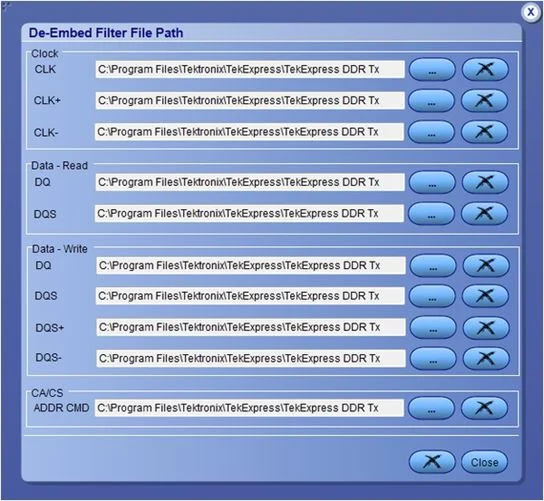

- De-embedding support for Clock, Command Address, Data Strobe, and data for both Write and Read traffic (or bursts)

- Number of UIs support for Clock and Read/Write data measurements

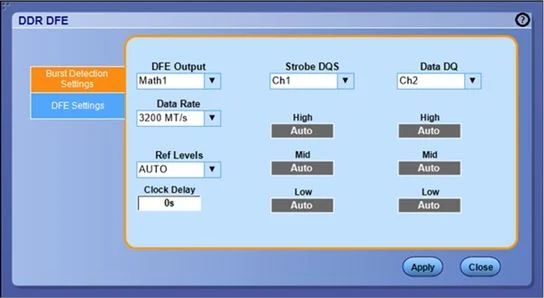

- Deploys DDR DFE standalone application, that can be launched from TekScope > Analyze > DDR DFE

- Support DFE for Write Data Eye measurements

- Multi-Run feature is applicable for all tests

- Save worst case waveform in known/TekExpress sessions

- Retain Vertical Scale support duringacquisition

- User-friendly measurement configurations

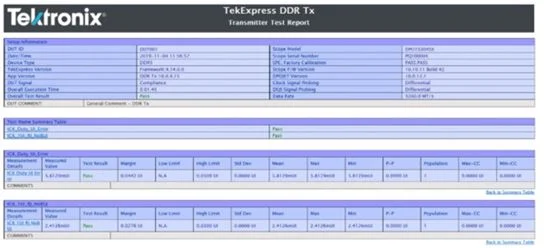

- Test report to reflect all the statistics of the measurement

- User can select the source and the channel in the acquisition panel

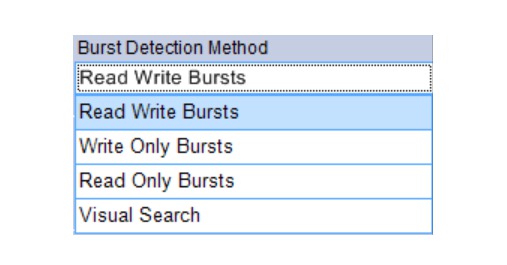

- Multiple Burst Detection Method supported - Read and Write, Write Only, Read Only, and Visual Search

- Diamond shape mask and margin analysis for Write Data Eye measurement

Applications

Tektronix provides the most comprehensive solution to serve the needs of the engineers designing DDR silicon for server, computer, graphics systems, mobile, embedded systems, and for those who are validating the physical-layer compliance of DDR Memory Compliance Test Specification.

The Tektronix option DDR5SYS (TekExpress DDR Tx) includes compliance and debug solution for the following:

- DRAM components

- Data Buffer/RCD components

- System boards

- Embedded systems

- Servers and Client/Desktop

The Tektronix option DDR5SYS is compatible with the following Tektronix oscilloscope models:

- DPO71604SX, DPO72304SX, DPO73304SX

- Non-ATI channels of DPS75004SX, DPS75904SX, DPS77004SX

- MSO72304DX, MSO72504DX, MSO73304DX, DPO72304DX, DPO72504DX, DPO73304DX

The above-mentioned Tektronix oscilloscopes are designed to meet the challenges of the next generation memory standards and provide the industry’s leading vertical noise performance with the highest number of effective bits (ENOB) and flattest frequency response for oscilloscopes in their class.

DDR5 system level tests

The Tektronix TekExpress DDR Tx solution reduces the effort and accelerates the compliance testing for DDR systems and devices with several unique and innovative capabilities.

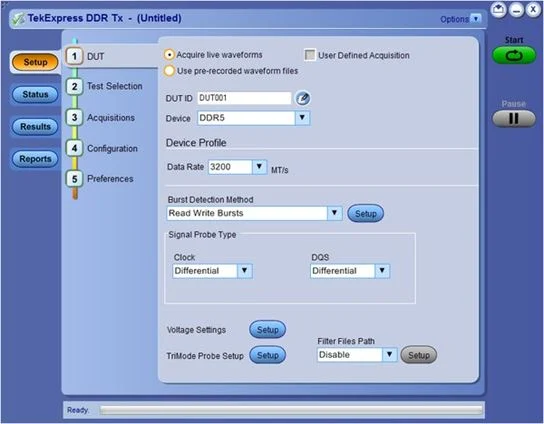

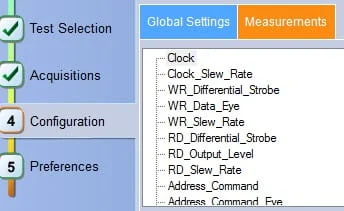

The TekExpress DDR Tx application provides a simple, step-by-step, and easy-to-use interface to speed up the testing process. User can select the memory technology of interest in Device, Data Rate, Burst Detection Method, select the probing configuration used for Clock, and strobe in the Setup DUT panel, in the next step perform the test selection as per measurement group (Clock, Command Address, Data Strobe, and Data for both Read and Write traffic (or bursts)) and individual measurements within the group provide different methods of Burst detection.

Acquisitions

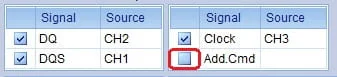

The TekExpress DDR Tx application comes with a unique feature to select or deselect the signal. Once the signal is selected in the acquisition panel, the user can select the signal source connected to the oscilloscope.

De-embed filters

Easily de-embed the interposer and the probe effects by applying suitable de-embed filters within the DDR5 standard.

Comprehensive measurements

The option DDR5SYS adds a long list of JEDEC specific measurements for DDR5 memory standards. The TekExpress DDR Tx application covers Electrical measurements, Timing measurements, and Eye Diagram measurements as per the JEDEC standards.

Automated Read and Write Burst detection

The TekExpress DDR Tx provides different ways to detect the burst cycles that are used to perform measurements:

- Read Write Bursts – when the DUT traffic is configured to send both Read and Write bursts then this method is used for burst detection.

- Write Only – when the DUT traffic is configured to send all Write Bursts then this method is used for burst detection.

- Read Only – when the DUT traffic is configured to send all Read Bursts then this method is used for burst detection.

- Visual Search – defining Visual Trigger areas to identify and gate area of interest for measurements

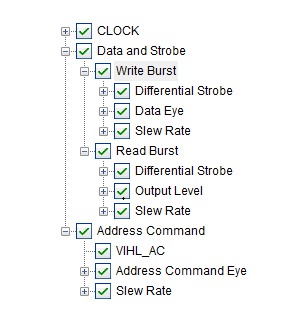

Test selection

The TekExpress DDR Tx test selection panel allows the user to select the various measurements supported by the application.

-

Supports 52 measurements of DDR5 System Transmitter Tests as per DDR5 JEDEC specification:

- 21 Clock measurements

- 09 Write Burst measurements

- 01 Write Data Eye measurement

- 13 Read Burst measurements

- 08 Command and Address measurements

Configurations

Ease of use measurement configuration to configure measurements by group instead of running through all the 50+ measurements.

DDR DFE standalone plugin

The DDR5 application supports data rates from 3200 MT/s to 6400 MT/s. This increase in the data rate is realized without the need for differential signaling at the DQ pins i.e. the DQ bus is single-ended – same as DDR3/4. However, due to the many impedance mismatched points that exist along with the memory subsystem, ISI due to reflections are expected to increase. At data rates >= 4800 MT/s, the data eye at the DRAM ball is expected to be closed. A 4-tap DFE is implemented in the DDR5 DRAM Rx to help equalize the DQ signals and open the data eyes after the data is latched by the receiver.

The TekExpress DDR Tx application provides DDR DFE as a standalone software application in Tektronix’s performance scopes. It is used to perform 4 tap DFE operation on the DDR5 write burst signals coming from the DDR5 DUTs.

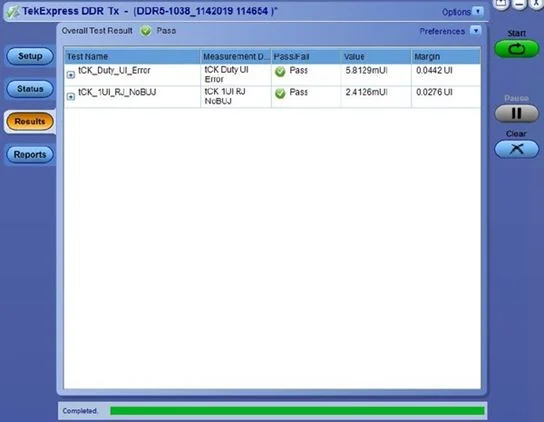

Results and reporting with waveform

The measurement configurations and JEDEC pass/fail limits are automatically applied for the selected measurements based on the memory specification and the selected speed grade. The results report includes DDR measurements statistical data, measurement plots, and the screenshot of the waveforms with the cursors. Hyperlinks within the report allows you to navigate between the sections.

When test execution is complete, the application automatically opens the Results panel and displays the summary of test results.

Verification versus debug

The TekExpress DDR Tx application provides a comprehensive set of JEDEC timing and electrical measurements for the DDR5 standard. Also, it provides access to the DPOJET advanced Jitter and Timing analysis engine that allows flexibility to reconfigure the existing measurements or to perform new measurements that are not defined by the JEDEC specification using new user-specified test limits. Additionally, it features logging, filters, histograms, and time trends that are available in DPOJET. The user can also switch between debug mode and the compliance mode.

Oscilloscope triggering and waveform identification

The Tektronix Pinpoint® trigger system provides the most comprehensive high-performance trigger system in the industry. The Pinpoint trigger system encompasses threshold and timing related triggers, Dual A and B Event Triggering, Logic Qualification, Window Triggering, and Reset Triggering.

The Advanced Search and Mark feature in the Tektronix MSO/DPO5000, DPO7000, and MSO/DPO70000 Series oscilloscopes find unique events in the waveforms. It scans acquired waveform data for multiple occurrences of an event and marks each occurrence.

The Search and Mark feature has a close relationship with the Pinpoint trigger system since they both can be used to discriminate signal characteristics. Search and Mark includes signal-shape discrimination features of the Pinpoint trigger system and extends them across live channels, stored data, and math waveforms.

The Visual Trigger makes the identification of the desired waveform events quick and easy by scanning all the acquired analog waveforms and comparing them with the geometric shapes on the display. By discarding the acquired waveforms which do not meet the graphical definition, Visual Triggering extends the oscilloscope’s trigger capabilities beyond the traditional hardware trigger system.