DDR4 在一些服务器和工作站上已经开始使用,DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以达到 3200Mb/s,这样高速的信号,对信号完整性的要求就更加严格,JESD79‐4 规范也对 DDR4 信号的测量提出了新的要求, 本文就要讨论一下 DDR4 测试面临的新挑战。

DDR4新的特性

DDR4 相比 DDR3,有很多新的变化,首先它的带宽提高了近一倍,最高达到 3200Mb/s,而且运行在更低的电压下,VDD 电压是 1.2V,这样可以在带宽提高的同时,不会提高系统的功耗。采用了新的颗粒架构,可以在单条内存上做到 16 个内存颗粒,内存封装和 DIMM 类型不变,但是内存的 Pin 脚数量有所变化,

DDR4 的 Pin 脚数达到 288Pin,Pin 脚间距更加小,更详细的对比,见下图

Fig.1 DDR4 和 DDR3 对比图

DDR4信号完整性测试新要求

在 DDR4 规范 JESD79‐4 中,对物理层信号测试要求有:DQ 眼图模板测试、抖动分析、电气特性测试,时序测试。相比 DDR3,DDR4 对眼图测试和抖动测试提出了新的要求 抖动测试

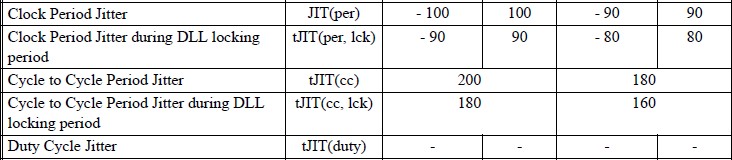

在 DDR3 的测试中,对 Clock 的抖动的测试要求是:Period Jitter、Cycle‐Cycle Jitter、 Duty Cycle Jitter。DDR3 的 Spec 中做了这样的推算:如果你的内存满足了规范要求的所有电气特性和时序特性,就可以一直正常的运行。现实状况下,这是没有考虑其他因素的理想情况,像随机抖动等也会影响产品的工作,而 DDR3 都没有对这些进行测试。

Fig.2 DDR3 Clock 抖动测试

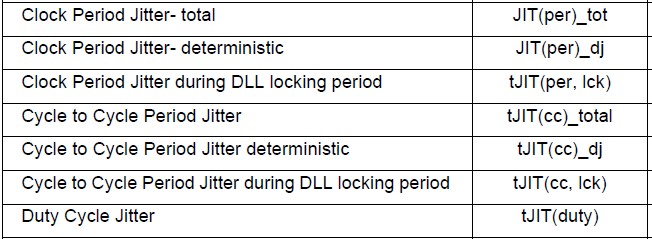

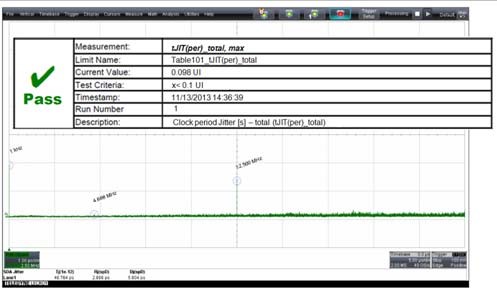

在 DDR4 的规范中,采用了更实际的方法来考虑这些因素,测试要求包含了随机抖动 Rj 和确定性抖动 Dj,在规范中,总体抖动 Tj 被定义为在一定误码率下的确定性抖动 Dj 和随机性抖动 Rj 的和,对抖动做了分解。Fig.5 是测试结果。

Fig.4 DDR4 Clock Jitter 要求

Fig.5 Lecroy Qualiphy‐DDR4 Jitter 测试结果

眼图模板测试

在 DDR3 测试中,眼图只是作为一个 Debug 的手段,不是强制要求测试,而且没有模板。但是在 DDR4 中,要求进行 DQ 输入接收端眼图模板测试,Fig.6 是眼图模板的定义,在 DDR4‐2133 及以下频率,TdIVW_total 和 TdIVW_dj 相等 VdIVW_total 和 VdIVW_dV 相等,从本质上,现在还没有在模板中定义随机成分。

Fig.6 DDR4 眼图模板定义

Fig.7 DDR4 DQ 眼图

DDR4 测试探测挑战

DDR4 的速率提升一倍,同时信号电压降低也接近一倍,这对测试探测技术提出了更高的要求。DDR4 规范中的所有测试都是定义在 BGA 或者 DIMM 的管脚处, 但是,在很多时候,我们很难直接探测到 BGA 管脚处,这样测出来的结果误差会非常大,解决方案是使用 Interposer 夹具或者虚拟探测技术,探测到理想点的波形。