DDR5内存规范和关键特性

内存技术也经历着不断更新迭代,如今,双倍数据速率(DDR)同步动态随机存取存储器(SDRAM 或直接称为 DRAM)技术,已成为几乎所有从高性能企业数据中心到注重功耗/面积的移动应用中的普遍的存储器。这一切都要归功于DDR 的高密度特性,其采用了电容器作为存储元件的简单架构具有高性能、低延迟、高访问寿命以及低功耗等特点。

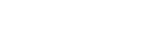

内存接口芯片是内存模组(又称内存条)的核心器件。作为服务器CPU 存取内存数据的必由通路,其主要作用是提升内存数据访问的速度及稳定性,满足服务器CPU 对内存模组日益增长的高性能及大容量需求。内存接口芯片应用于服务器内存条,在按技术进行的产品分类上遵循内存接口芯片技术标准,主要为 JEDEC(全球微电子产业的领导标准机构)之DDR 标准,例如DDR2,DDR3,DDR4,DDR5 等。

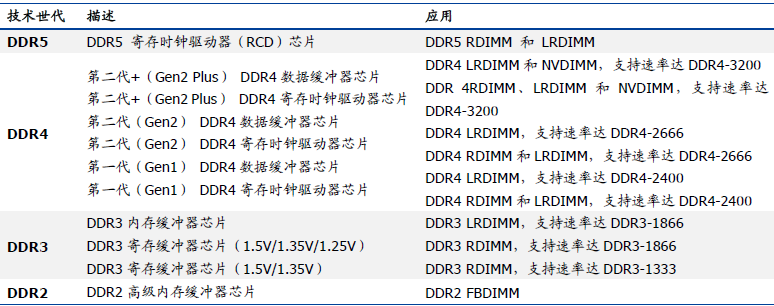

JEDEC(固态技术协会)定义中开发了三种 DDR 标准:标准DDR、移动 DDR 和图形 DDR,来帮助设计人员满足对内存的要求。JEDEC 目前在 DDR 类别中的最新一代是DDR5。随着JEDEC技术协会发布存储器标准DDR5 SDRAM的最终规范,这将标志着计算机存储器开发的一个重要里程碑。自90年代末以来,DDR的最新版本一直在驱动PC,服务器以及所有产品之间的发展,DDR5再次扩展了DDR内存的功能,使峰值内存速度提高了一倍,同时也大大增加了内存大小。

DDR5 将以较之 DDR4 更低的 I/O 电压 (1.1V) 和更高的密度(基于 16Gb DRAM 晶粒)支持更高的数据速率(高达 6400 Mb/s)。DDR5 DRAM 和双列直插式存储模块 (DIMM) 有望于今年投放市场。

本文概述了 DDR5 DRAM 的几个主要功能,设计人员可以将其部署在服务器、云计算、网络、笔记本电脑、台式机和消费类应用等类型的片上系统 (SoC) 中。

什么是标准 DDR?

具备高密度和高性能的标准 DDR DRAM 有各种型号和外形尺寸,支持 4 (x4) 或 8 (x8) 或 16 (x16) 位的数据宽度。终端应用可以将这些存储器用作分立式 DRAM 或 DIMM。

DIMM 是一款带有多个 DRAM 芯片的印刷电路板 (PCB) 模块,支持 64 或 72 位数据宽度。72 位 DIMM 称为纠错码 (ECC) DIMM,除支持 64 位数据外,还支持 8 位 ECC。

服务器、云和数据中心应用通常使用基于 4 个 DRAM 的 72 个 ECC DIMM,在获得更高密度的 DIMM 的同时还可支持更高的 RAS(可靠性、可用性、可维护性)功能。除此之外,这样的ECC DIMM还能缩短此类应用在存储器发生故障时的停机时间。

对比其他 8 bit 和 16 bit DRAM 的 DIMM 来说,这种方案价格较为便宜,所以此类产品被广泛用于台式机和笔记本电脑中。与此同时,还可以将这些存储器当作分立式 DRAM 来使用。因此,与其他 DDR 类别方案相比时,标准 DDR 通道宽度的灵活性就是其最大的优势。

DDR5 究竟有什么魅力?

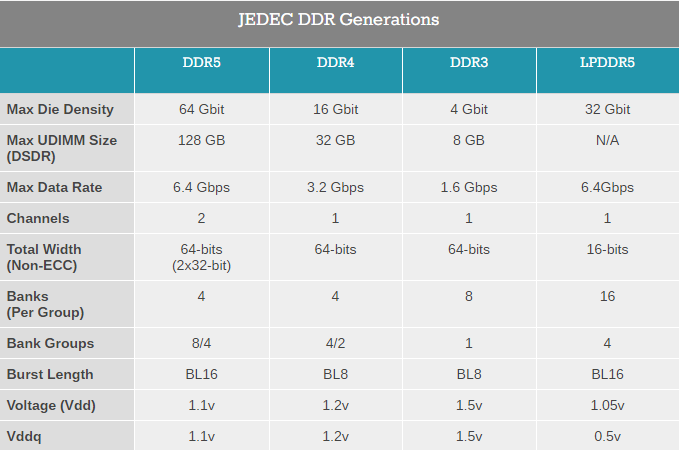

与 DDR4 相比,DDR5 新增特征包括:突发长度增加到16拍,其出色的刷新/预充电方案可实现更高的性能,可提高通道利用率的双通道 DIMM 架构,可在DDR5 DIMM 上集成稳压器,可增加的存储区分组,以及可命令/地址片内端接电阻 (ODT)等多种优势。表1将 DDR5 和 DDR4 DRAM/DIMM 的功能进行了对比。

表1:DDR5 对比 DDR4 DRAM/DIMM

除性能更强之外,DDR5 还引入多种 RAS 功能,以保持通道提速后的稳定性。这些 DDR5 通道稳定性的功能包括:占空比调节器 (DCA)、片上 ECC、DRAM 接收 I/O 均衡、RD 和 WR 数据的循环冗余校验 (CRC) 以及内部 DQS 延迟监控。以下是对这些功能的详细说明:

1. 用于补偿占空比失真的占空比调节器 (DCA)

占空比调节器支持主机通过调节 DRAM 内部的占空比来补偿所有 DQS(数据选通)/DQ(数据)引脚上的占空比失真。因此,DCA 功能巩固了读取数据的稳定性。

2. 强化 RAS 的片上 ECC

DDR5 DRAM 为每 128 位数据设置 8 位的 ECC 存储空间,使得片上 ECC 具有强大的 RAS 功能,可以保护存储器阵列免受单个数位错误的影响。

3. DRAM 获得 DQ 均衡以增加裕量

DDR5 DRAM 和 LPDDR5 DRAM 一样,也支持 WR 数据均衡。该功能在 DRAM 端为 WR DQ 打开了新的局面,不仅可以保护通道免受符号间干扰 (ISI) 的影响,增加裕量,还可实现更高的数据速率。

4. RD/WR 数据的循环冗余校验 (CRC)

DDR4 仅支持写数据使用的 CRC,而 DDR5 将 CRC 的适用范围扩展到读数据,从而提供额外保护,避免通道出错。

5. 内部 DQS 延迟监控

内部 DQS 延迟监控机制支持主机调整 DRAM 延迟来补偿电压和温度变化。以 DDR5 速度运行的主机可以使用此功能定期重新训练通道,补偿 DRAM 中延迟引起的 VT 变化。

6. DDR5带来的挑战

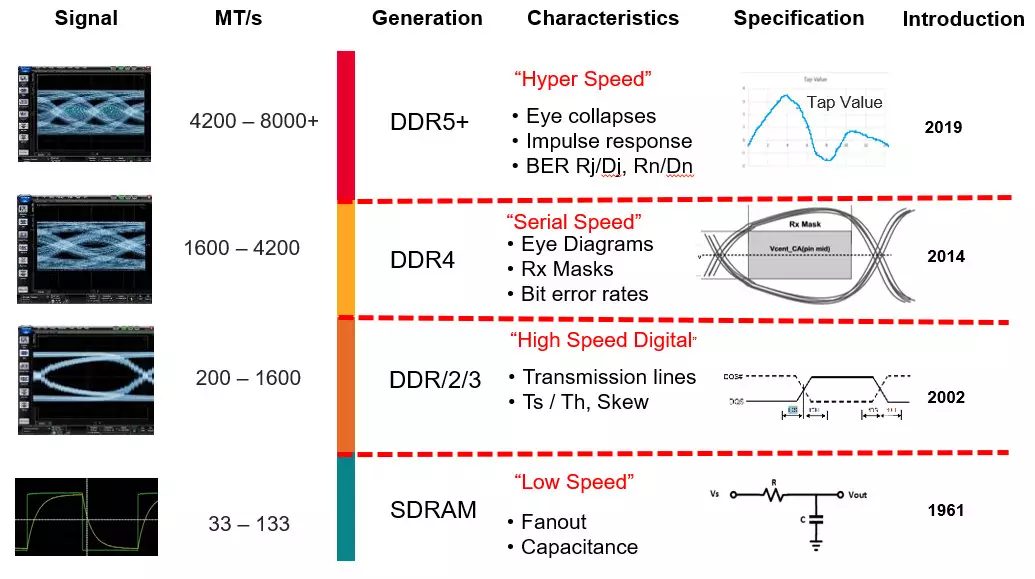

从DDR的发展图中可以看到,DDR的传输速率在成倍提升,而其迭代速度也在不断加快。

DDR5的速率最高超过8.4GT/s,达到了前代DDR4最高速率的两倍。更高的速率,带来出色性能的同时,不可避免的提升了设计的困难。

-

DDR信号较多,走线较为密集,随着信号速率的增加,传输线之间的串扰也会随之增加。

-

除了串扰外,抖动也是不能被忽视的问题。

-

由于传输线的频率选择特性,频率越高,传输线的插入损耗也会随之增加,信号的衰减和码间干扰的现象也会更加严重。

总结

为满足目标应用的要求,设计人员在为自己的设计选择最佳片外存储器技术时DDR 已成为了必选技术方案之一。从最早的400 Mbps 的 DDR 发展到了当今的 6400 Mbps 的 DDR5,每一代 DDR 的数据速率都翻倍增长。

随着内核数量的增加,DDR5 提供了更高的密度(包括双通道 DIMM 拓扑),从而保证通道效率和其性能,这些优势对于适合服务器、云计算、网络、笔记本电脑、台式机和消费类等应用的 SoC 最为重要。无论设计人员选择哪种 DDR DRAM 技术,都必须在 SoC 中部署兼容的接口 IP 解决方案,以实现与 DRAM 之间的必要连接。