DDR5中I3C的协议测试

Serial Presence Detect (SPD) is a standardized method to automatcally access the informaton about DDR3/4/5 memory modules. When a electronic system us powered on, it starts doing automatcally confguring the system by identfying diferent hardware components. SPD is a feature in DDR3/4/5 enables the electronic system to know the DDR memory details and its tming informaton. DDR3/4 memory modules use SM Bus to provide this informaton. In case latest very high speed memory DDR5 uses low voltage signals (1V) I3C interface to read the memory details and its tming informaton.

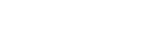

Fig 1. Typical I3C Bus architecture in DDR5 based system design

Typical I3C bus architecture is shown in Fig.1. When host controller is interfaced DDR5 modules using SPD5 hub. During the design and testng stage, it can be very challenging to monitor all the I3C bus in this architecture using of the shelf oscilloscopes.

Some of the key requirements to debug these designs as below

- Need logic analyser which can work with 1V signal amplitude.

- It should be possible to acquire diferent I3C logic actvites at the same tme.

- It is should also possible decode all these I3C buses may be operatng at diferent rate varying from 100KHz to 12.5MHz

- Monitor specifc event in the I3C bus

Prodigy Technovatons has developed industry frst mult-channel I3C decode soluton on the existng logic analyser. It has following capabilites.

- Identfes logic levels at 1V signal amplitude.

- Decode eight I3C buses at the same tme.

- Power full trigger capabilites

- Asynchronous sampling1GS/sec enables capturing varying clack rate I3C protocol events

PGY-LA-Mult-I3C is a 16 Channel logic analyser. Which has the following key capabilites

- 1GS/Sec asynchronous sampling capabilites

- Eight I3C Bus decoding capabilites

- Trigger on I3C Protocol Packet content

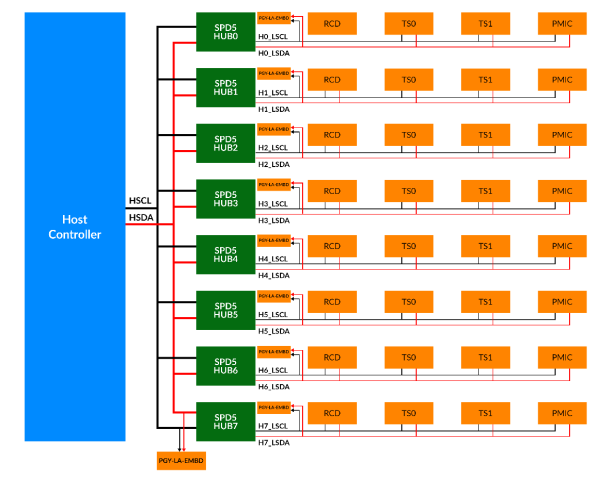

Multchannel I3C Protocol decode analysis result view as shown in fg3.

Fig. 2. Listng of Mult I3C channel decode and digital tming diagram

Listng window list decodes the i3C packets from diferent I3C bus and displays it. Timestamp is used to list packet in the order so that user can the events happening with respect to the tme.

Sofware also displays the tming waveform with bus diagram. Bus diagram will have each I3C packet informaton for easy debug purposes.

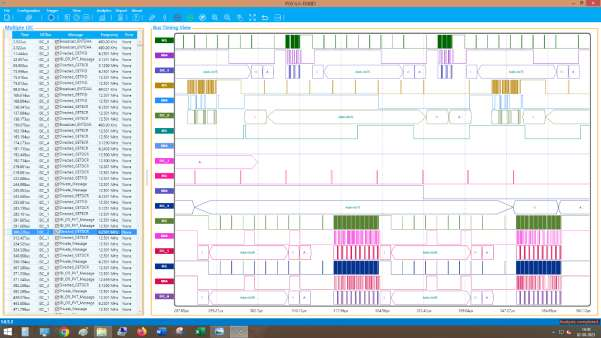

To capture the trafc at specifc event, user can set the trigger conditon based on I3C Protocol packet content.

Fig. 3. I3C protocol Aware Trigger GUI

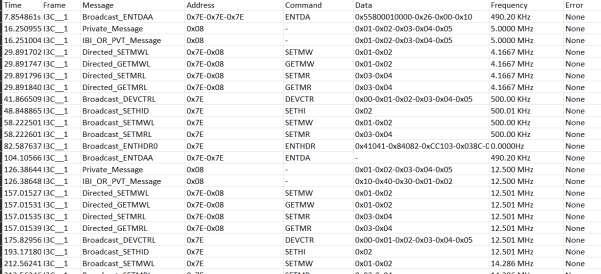

User can export this data to fle in CSV format. This DATA can be viewedExcel sofware for further analysis

Fig. 4. CSV export in Excel sofware

Exported data will tme stamp, I3C bus name, protocol packet content and frequency of operaton. T

PGY-LA-Mult-I3C provides most comprehensive soluton address the DDR5 system requirements for serial peripheral detect bus. It can decode all eight channels with listng and tming diagram view. Abilites to export this data makes it most convenient to use it.

Prodigy Technovatons provides most comprehensive soluton to develop I3C Technology. Following are products.